Pokud programujete mikrokontroléry od firmy STM (STM32F4, STM32F0, STM32L1) pomocí Standard Pheripheral Library, tak se vám možná nelíbí velikost výsledného kódu. Ovšem pokud budete přímo nastavovat registry, mohou se vám objevit různé problémy a hledání příčiny už není tak triviální. Dnes vám popíšu, jak se programuje USART na mikrokontroléru STM32L100, ale protože jde o základní periferii, portování na jiný mikrokontrolér nebude nijak složité.

Článek byl inspirován stránkou joudove.8u.cz.

Jak vypadá základní rámec protokolu UART, si můžete najít kdekoliv. Popisování jednotlivých bitů registrů také nebudu vyjmenovávat (a překládat), protože jako programátoři byste měli minimálně anglickému datasheetu rozumět. Jenom upozorním, na „záludné“ registry, kde jsem dělal (nebo i vy) chyby.

První moje chyba byla:

tedy chybějící znak |

To znamená, že přímo nastavujete tyto piny. Smůla ovšem je, že na stejném portu se nachází programovací rozhraní SWD.

Vývojové prostředí Keil vám oznámí po nahrání programu v terminálu:

Internal command error

A pokud chcete nahrát program, nahrávání skončí s hláškou: No target connected a poté Error: Flash Download failed – Target DLL has been cancelled

Pokud se podíváte do Flash -> Configure Flash Tools -> Debug -> Settings (u výběru programátoru) -> Vypíše hlášku v okně SW Device: No Cortex-M SW Device Found

V tomto okamžiku už s tím nic neuděláte a budete to muset opravit (o tom v textu níže).

Pokud nahráváte program pod vývojovým prostředím Atollic TrueStudio, ten vám vypíše chybu Remote failure reply: E31. Atollic se vás v terminálu zeptá, jestli chcete ten proces zabít. Zmáčknete „y“ – yes. Mikrokontrolér je dále viditelný a vy si musíte opravit chybu ve vašem kódu.

Ale jak to opravit v IDE Keil? Buď zapnete Atollic TrueStudio a naprogramujete to tam NEBO si stáhnete utilitu ST-LINK, tam zaškrtnete v Target -> Settings -> Mode: Connect Under Reset nebo poslední a nejsnazší varianta:

Opravíte si v IDE Keil váš kód, abyste nenastavovali celý PORT, tedy přidáte |, zkompilujete program, na Discovery desce zmáčknete tlačítko RESET a po malé chvíli (cca 0.5s) zmáčknete tlačíko „Load“ v Keil a potom pustíte tlačítko RESETu na desce. Poté se kód nahraje do mikrokontroléru.

Poznámka z komentářů: Popřípadě v nastavení programátoru zaškrtnete „Connect under reset“. Za komentář děkujeme.

Pokud jste program správně opravili, tak ve Flash -> Configure Flash Tools -> Debug -> Settings (u výběru programátoru) -> Vypíše hlášku v okně SW Device: se vám objeví váš mikrokontrolér.

Přejdeme k další chybě a to je nastavení registru AFR – tedy nastavení alternativních funkcí.

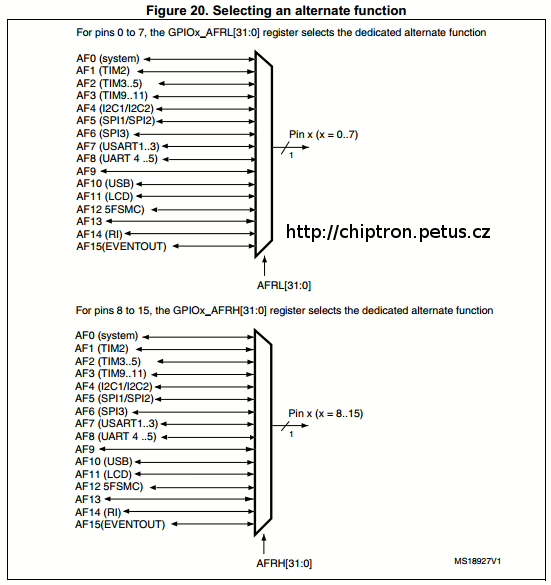

Podle níže zobrazeného obrázku vidíte, že USART1 se nachází na AF7, což znamená, že nastavení PINu pro alternativní funkci musíte nastavit na hodnotu 7.

Protože každý PIN může mít až 16 (0 – 15) alternativních funkcí, jsou každému PINu vyhrazeny 4 bity v 32 bit registru AFR. Registr AFR[0] je registr pro PINy 0 – 7 a AFR[1] je pro PINy 8 – 15.

A nakonec poslední problém byl správné nastavení BRR tedy Baud rate register. Registr se dělí na dvě části – 4 bity pro tzv. Fraction a 12 bitů pro tzv. Mantissu. Vzorec je jednoduchý a naleznete ho zde: http://joudove.8u.cz

Použijte naši kalkulačku na výpočet Baud Rate!

A nakonec celý kód pro USART – mikrokontrolér přijme znak a pošle ho zpátky.

MAIN.C

a ještě system_stm32l1xx.c

Žádné sociální komentáře k dispozici.