Jazyk VHDL je úplně jiný než kterýkoli jiný jazyk používaný v mikrokontrolérech. Každý příkaz se provádí paralelně. Tutoriálů je docela dost, takže si myslím, že základy můžete čerpat kdekoli z internetu.

Například zde: http://www.prochazka.profitux.cz/index.php?p=vhdl

nebo si můžete koupit knihu: Číslicové systémy a jazyk VHDL, od autorů: Jiří Pinker a Martin Poupa z roku 2006, nakladatelství BEN.

Jako vývojové prostředí budeme používat ModelSim od Altery.

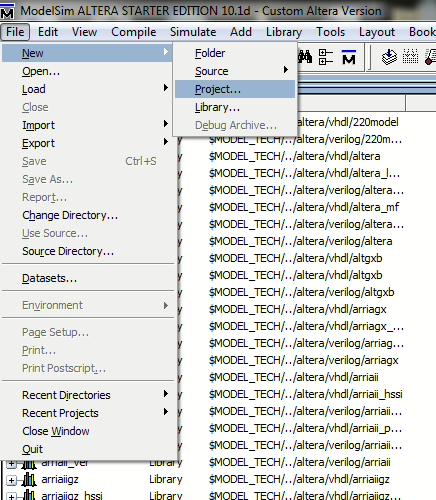

Nejprve si založíme projekt:

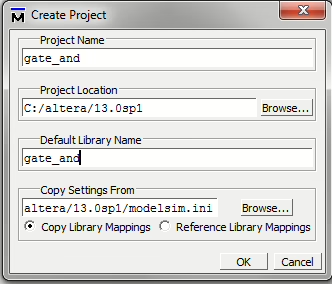

Poté zadáme název nového projektu.

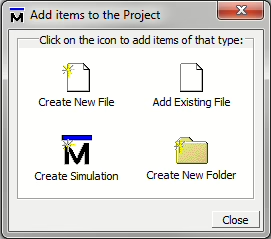

Po odkliknutí budeme dotázáni, zda má vytvořit nový soubor nebo přidat existující.

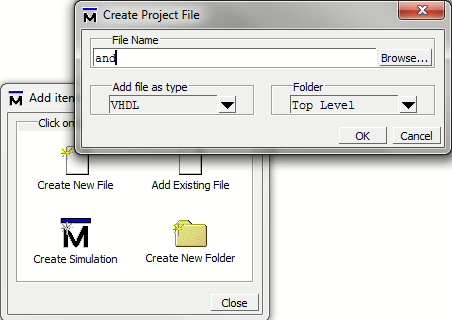

Při odkliknutí „Create New File“ se objeví okno pro zadání názvu souboru.

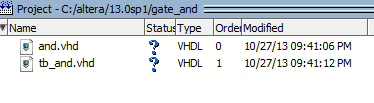

Založíme si rovnou 2 soubory a to „and.vhdl“ a „tb_and.vhd“. TB – test Bench, soubor, testující chování námi navrženého obvodu. Jak můžete vidět, v kolonce „Status“ jsou otazníky, to znamená soubory ještě nebyli zkompilovány.

Soubor and.vhd

Soubor tb_and.vhd

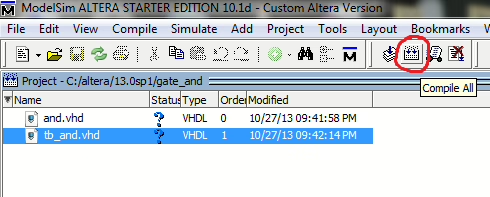

Kompilaci souborů provedete tlačítkem Compile All.

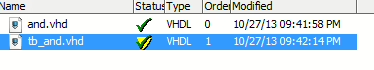

Pokud kompilace proběhne v pořádku, objeví se ve kolonce „Status“ fajfka.

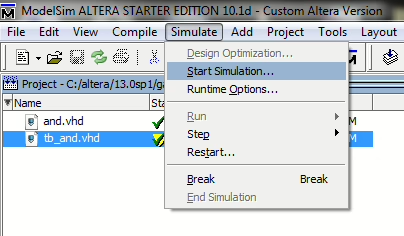

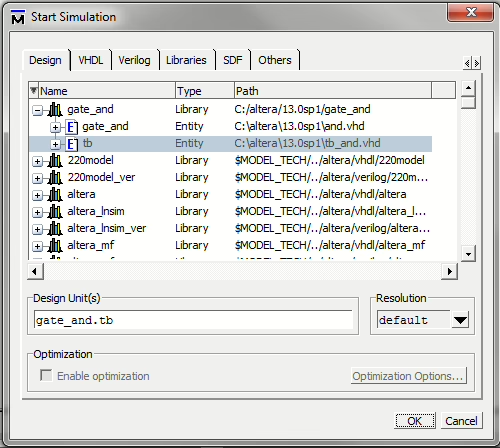

Spuštění simulace provedeme v záložce „Simulate“ -> „Start Simulation“.

Objeví se okno, kde vybereme název našeho projektu a označíme složku „tb“ a odklikneme OK.

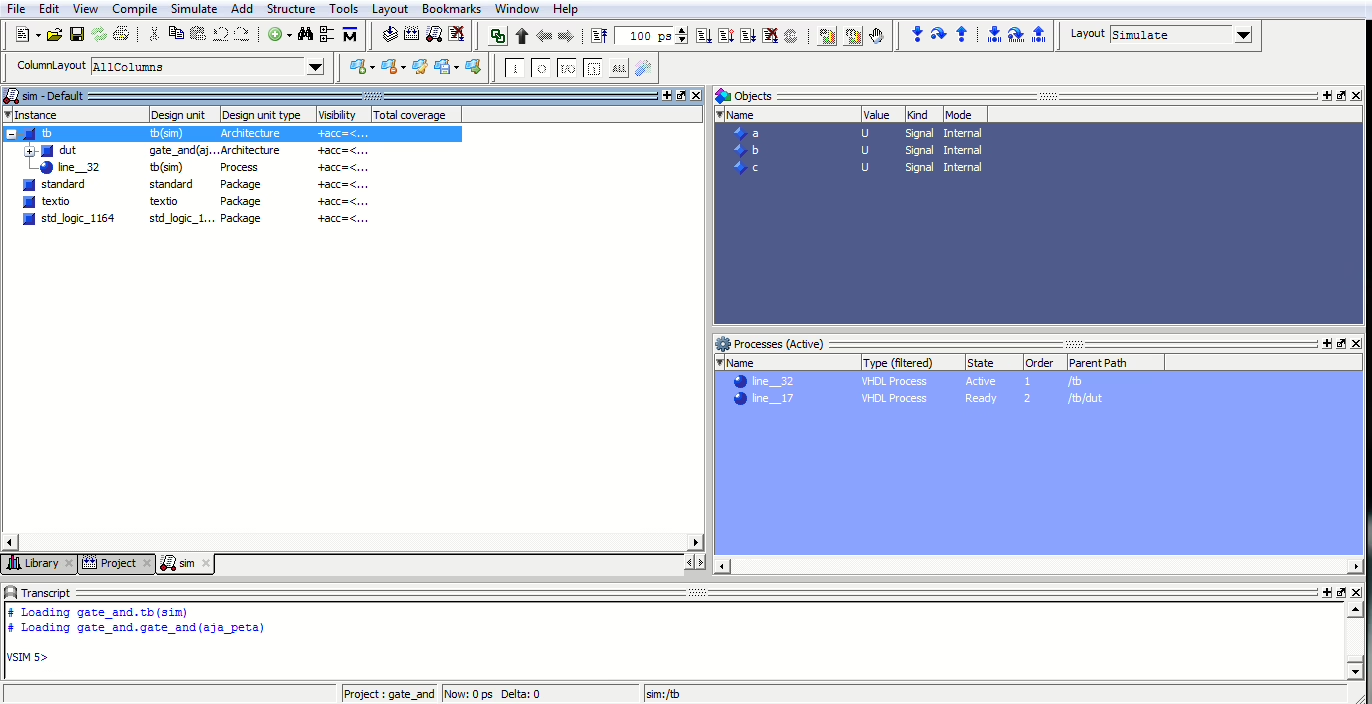

Objeví se nové okno, kde vidíte (vpravo) všechny signály.

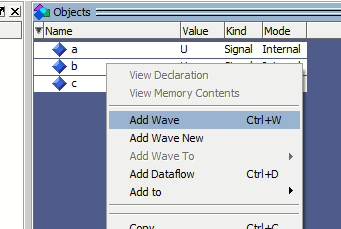

Označíme všechny simulace, klikneme pravým tlačítkem myši a dáme „Add Wave“ nebo „Ctrl + W“

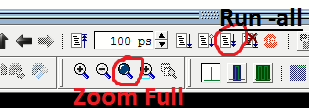

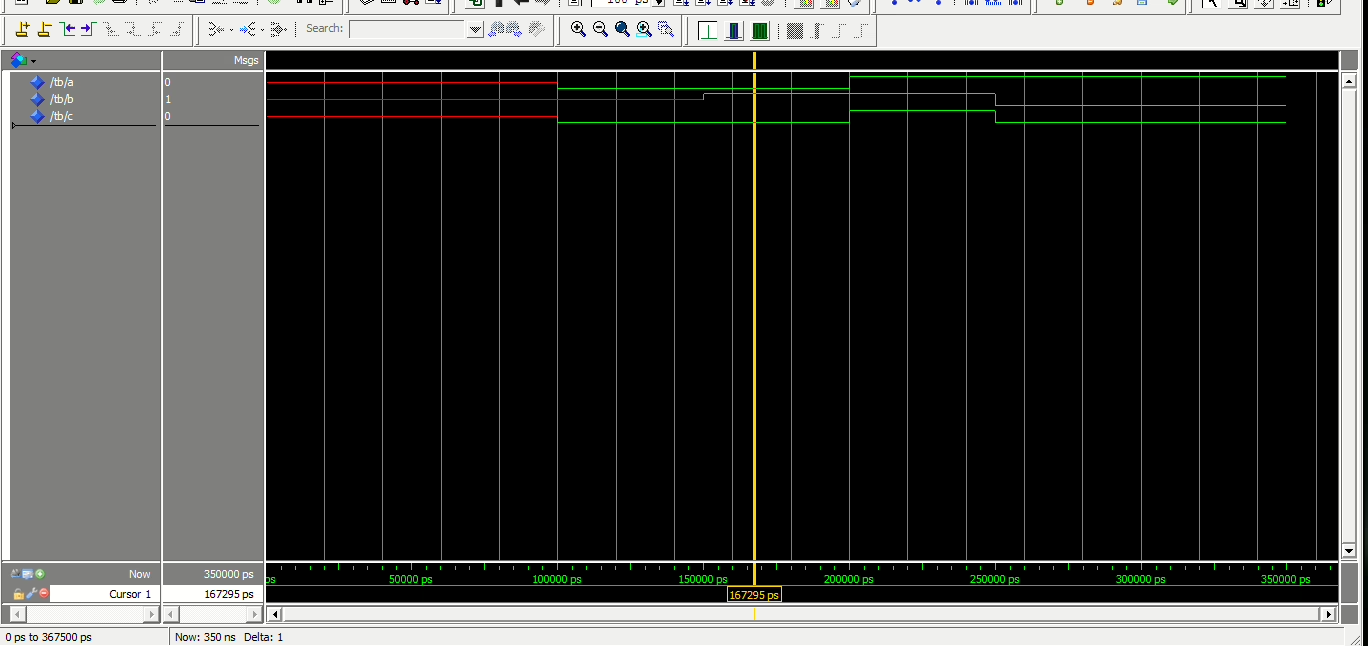

Otevře se nové okno se simulací, kde pro spuštění simulace klikneme na tlačítka „Run -All“ a poté odzoomujeme tlačítkem „Zoom Full“

Na následujícím obrázku vidíte spuštěnou simulaci. Kliknutím myši na ono simulace se objeví kurzor, který vlevo (/tb/a např) ukazuje ukazuje aktuální hodnotu signálů.

Žádné sociální komentáře k dispozici.