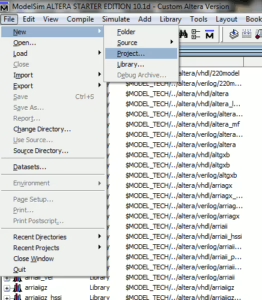

Další příklad kódu ve VHDL pro FGPA. Tentokrát 8bitový čítač/counter. Jsou zde dva zdrojové kódy (i testbenche), u kterých je vysvětlen rozdíl mezi podmínkama na vstupu „reset“. Článek je doplněn o dva obrázky vysvětlující každou situaci.

Článek – VHDL – 8bit čítač/counter

Autor: Petr Šrámek

Tagy:

Ukaž světu,

že jsi Maker!

Koupit tričkože jsi Maker!

Související články

Vývojové kity/desky (nebo také development board) jsou velmi populární a každý den nějaký přibude.

Máte pásek s desítkami součástek a potřebujete je přepočítat? Ano, stačí vám pravítko a změřit počet součástek na určité délce, ale spolehlivé a rychlé to určitě není.

Trendy

# esphome

# rtl-sdr

# meshcore

# expLORA

# meshtastic

# riden

# fnirsi

# živý obraz

# meteostanice

# sensirion SEN6x

# alzament pla+

# home assistant

# 3d tisk

# měření teploty

# pájecí pinzeta

# vláčkodráha

# CH32

# pájení SMD

# step-down měnič

# ESP32 cam

# nabíjecí baterie

# novinky v českých eshopech

# bastltířský kalendář

# omnifixo

# micropython

# makerfaire

# stm32

# arduino

Žádné sociální komentáře k dispozici.