Další příklad kódu ve VHDL pro FGPA. Tentokrát 8bitový čítač/counter

Budou zde zobrazeny dva zdrojové kódy, v prvním je podmínka:

if (reset =’1′) then

to znamená, že čítač bude v resetu, dokud bude vstup „reset“ v logické 1.

Ve druhém příkladu je tato podmínka upravena:

if (reset =’1′ AND reset’event) then

to znamená, že reset vyresetuje čítač pouze tehdy, pokud bude vstup „reset“ v logické 1 A ZÁROVEŇ nastane na tomto vstupu změna stavu.

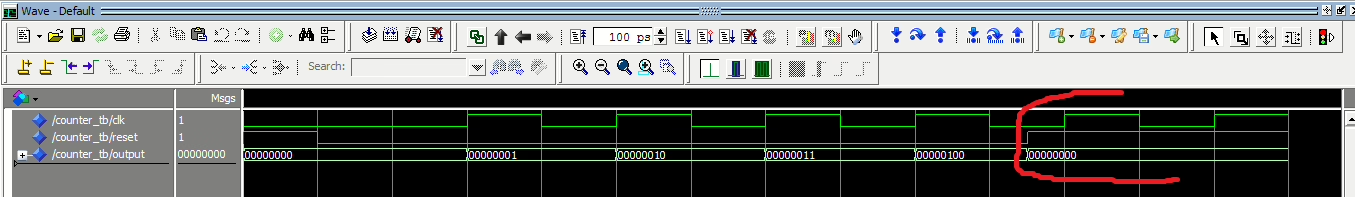

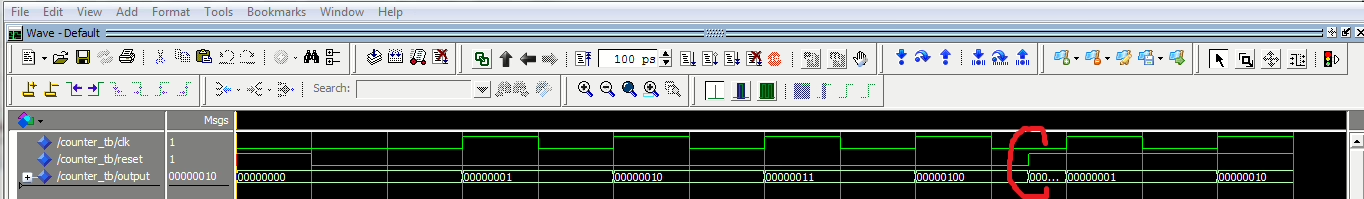

Obě tyto podmínky vysvětlují i obrázky ze simulace.

První příklad:

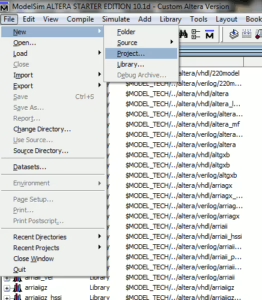

counter.vhd

counter_tb.vhd

Druhý příklad:

counter.vhd

counter_tb.vhd

Žádné sociální komentáře k dispozici.